# Programmable Logic Device Family

January 1998, ver. 4 Data Sheet

## Features...

- Advanced Multiple Array MatriX (MAX®) 5000 architecture combining speed and ease-of-use of PAL devices with the density of programmable gate arrays

- Complete family of high-performance, erasable CMOS EPROM erasable programmable logic devices (EPLDs) for designs ranging from fast 28-pin address decoders to 100-pin LSI custom peripherals

- 600 to 3,750 usable gates (see Table 1)

- Fast, 15-ns combinatorial delays and 76.9-MHz counter frequencies

- Configurable expander product-term distribution allowing more than 32 product terms in a single macrocell

- 28 to 100 pins available in DIP, J-lead, PGA, and QFP packages

- Programmable registers providing D, T, JK, and SR flipflop functionality with individual clear, preset, and clock controls

- Programmable security bit for protection of proprietary designs

- Software design support featuring the Altera® MAX+PLUS® II development system on 486- or Pentium-based PCs, and Sun SPARCstation, HP 9000 Series 700/800, and IBM RISC System/6000 workstations

| Feature                   | EPM5032 | EPM5064 | EPM5128 | EPM5130 | EPM5192 |

|---------------------------|---------|---------|---------|---------|---------|

| Usable gates              | 600     | 1,250   | 2,500   | 2,500   | 3,750   |

| Macrocells                | 32      | 64      | 128     | 128     | 192     |

| Logic array blocks (LABs) | 1       | 4       | 8       | 8       | 12      |

| Expanders                 | 64      | 128     | 256     | 256     | 384     |

| Routing                   | Global  | PIA     | PIA     | PIA     | PIA     |

| Maximum user I/O pins     | 24      | 36      | 60      | 84      | 72      |

| t <sub>PD</sub> (ns)      | 15      | 25      | 25      | 25      | 25      |

| t <sub>ASU</sub> (ns)     | 4       | 4       | 4       | 4       | 4       |

| t <sub>co</sub> (ns)      | 10      | 14      | 14      | 14      | 14      |

| f <sub>CNT</sub> (MHz)    | 76.9    | 50      | 50      | 50      | 50      |

# ...and More Features

- Programming support with Altera's Master Programming Unit (MPU) or programming hardware from third-party manufacturers

- Additional design entry and simulation support provided by EDIF, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and Viewlogic

# General Description

The MAX 5000 family combines innovative architecture and advanced process technologies to offer optimum performance, flexibility, and the highest logic-to-pin ratio of any general-purpose programmable logic device (PLD) family. The MAX 5000 family provides 600 to 3,750 usable gates, pin-to-pin delays as fast as 15 ns, and counter frequencies of up to 76.9 MHz. See Table 2.

| Table 2. MAX 5000 Device Speed Grades |          |       |                        |          |          |  |  |  |

|---------------------------------------|----------|-------|------------------------|----------|----------|--|--|--|

| Device                                |          | Spe   | ed (t <sub>PD1</sub> ) |          |          |  |  |  |

|                                       | 15 ns    | 20 ns | 25 ns                  | 30 ns    | 35 ns    |  |  |  |

| EPM5032                               | <b>✓</b> | ✓     | <b>✓</b>               |          |          |  |  |  |

| EPM5064                               |          |       | <b>✓</b>               | <b>✓</b> | <b>✓</b> |  |  |  |

| EPM5128                               |          |       | <b>✓</b>               | ✓        | ✓        |  |  |  |

| EPM5130                               |          |       | <b>✓</b>               |          | <b>✓</b> |  |  |  |

| EPM5192                               |          |       | <b>✓</b>               |          | <b>✓</b> |  |  |  |

The MAX 5000 architecture supports 100% TTL emulation and high-density integration of multiple SSI, MSI, and LSI logic functions. For example, an EPM5192 device can replace over 100 74-series devices; it can integrate complete subsystems into a single package, saving board area and reducing power consumption. MAX 5000 EPLDs are available in a wide range of packages (see Table 3), including the following:

- Windowed ceramic and plastic dual in-line (CerDIP and PDIP)

- Plastic J-lead chip carrier (PLCC)

- Windowed ceramic pin-grid array (PGA)

- Plastic quad flat pack (PQFP)

| Device  |                        |      | Pin Count   |             |             |

|---------|------------------------|------|-------------|-------------|-------------|

|         | 28                     | 44   | 68          | 84          | 100         |

| EPM5032 | CerDIP<br>PDIP<br>PLCC |      |             |             |             |

| EPM5064 |                        | PLCC |             |             |             |

| EPM5128 |                        |      | PLCC<br>PGA |             |             |

| EPM5130 |                        |      |             | PLCC        | PGA<br>PQFP |

| EPM5192 |                        |      |             | PLCC<br>PGA |             |

MAX 5000 EPLDs have between 32 and 192 macrocells that are combined into groups called logic array blocks (LABs). Each macrocell has a programmable-AND/fixed-OR array and a configurable register that provides D, T, JK, or SR operation with independent programmable clock, clear, and preset functions. To build complex logic functions, each macrocell can be supplemented with shareable expander product terms ("shared expanders") to provide more than 32 product terms per macrocell.

The MAX 5000 family is supported by Altera's MAX+PLUS II development system, a single, integrated package that offers schematic, text—including the Altera Hardware Description Language (AHDL)— and waveform design entry; compilation and logic synthesis; simulation and timing analysis; and device programming. The MAX+PLUS II system provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX workstation-based EDA tools. The MAX+PLUS II software runs on 486- and Pentium-based PCs, and Sun SPARCstation, HP 9000 Series 700/800, IBM RISC System/6000 workstations.

For more information, go to the MAX+PLUS II Programmable Logic Development System & Software Data Sheet in this data book.

# Functional Description

This section provides a functional description of MAX 5000 EPLDs, which have the following architectural features:

- Logic array blocks

- Macrocells

- Clocking options

- Expander product terms

- Programmable interconnect array

- I/O control blocks

The MAX 5000 architecture is based on the concept of linking high-performance, flexible logic array modules called logic array blocks (LABs). Multiple LABs are linked via the programmable interconnect array (PIA), a global bus that is fed by all I/O pins and macrocells. In addition to these basic elements, the MAX 5000 architecture includes 8 to 20 dedicated inputs, each of which can be used as a high-speed, general-purpose input. Alternatively, one of the dedicated inputs can be used as a high-speed global clock for registers.

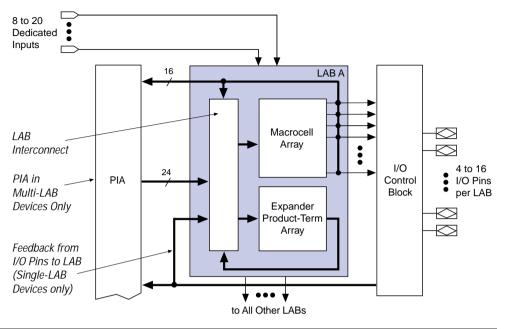

## **Logic Array Blocks**

MAX 5000 EPLDs contain 1 to 12 LABs. The EPM5032 has a single LAB, while the EPM5064, EPM5128, EPM5130, and EPM5192 contain multiple LABs. Each LAB consists of a macrocell array and an expander product-term array. See Figure 1. The number of macrocells and expanders in the arrays varies with each device.

Figure 1. MAX 5000 Architecture

Macrocells are the primary resource for logic implementation. Additional logic capability is available from expanders, which can be used to supplement the capabilities of any macrocell. The expander product-term array consists of a group of unallocated, inverted product terms that can be used and shared by all macrocells in the LAB to create combinatorial and registered logic. These flexible macrocells and shareable expanders facilitate variable product-term designs without the inflexibility of fixed product-term architectures. All macrocell outputs are globally routed within an LAB via the LAB interconnect. The outputs of the macrocells also feed the I/O control block, which consists of groups of programmable tri-state buffers and I/O pins. In the EPM5064, EPM5128, EPM5130, and EPM5192 devices, multiple LABs are connected by a PIA. All macrocells feed the PIA to provide efficient routing for high-fan-in designs.

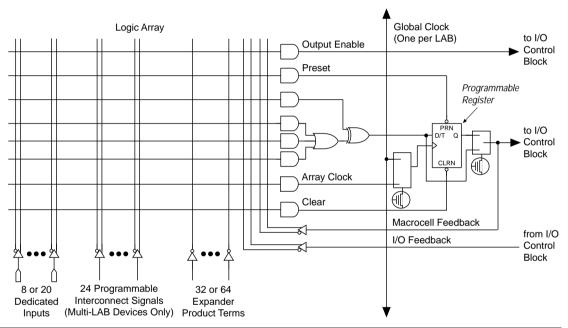

#### Macrocells

The MAX 5000 macrocell consists of a programmable logic array and an independently configurable register (see Figure 2). The register can be programmed to emulate D, T, JK, or SR operation, as a flow-through latch, or bypassed for combinatorial operation. Combinatorial logic is implemented in the programmable logic array, in which three product terms that are <code>ORed</code> together feed one input to an <code>XOR</code> gate. The second input to the <code>XOR</code> gate is used for complex <code>XOR</code> arithmetic logic functions and for De Morgan's inversion. The output of the <code>XOR</code> gate feeds the programmable register or bypasses it for combinatorial operation.

Figure 2. MAX 5000 Device Macrocell

Additional product terms—called secondary product terms—are used to control the output enable, preset, clear, and clock signals. Preset and clear product terms drive the active-low asynchronous preset and asynchronous clear inputs to the configurable flipflop. The clock product term allows each register to have an independent clock and supports positive- and negative-edge-triggered operation. Macrocells that drive an output pin can use the output enable product term to control the active-high tri-state buffer in the I/O control block.

The MAX 5000 macrocell configurability makes it possible to efficiently integrate complete subsystems into a single device.

### Clocking Options

Each LAB supports either global or array clocking. Global clocking is provided by a dedicated clock signal (CLK) that offers fast clock-to-output delay times. Because each LAB has one global clock, all flipflop clocks within the LAB can be positive-edge-triggered from the CLK pin. If the CLK pin is not used as a global clock, it can be used as a high-speed dedicated input.

In the array clocking mode, each flipflop is clocked by a product term. Any input pin or internal logic can be used as a clock source. Array clocking allows each flipflop to be configured for positive- or negative-edge-triggered operation, giving the macrocell increased flexibility. Systems that require multiple clocks are easily integrated into MAX 5000 EPLDs.

Each flipflop in an LAB can be clocked by a different array-generated clock; however, global and array clocking modes cannot be mixed in the same LAB.

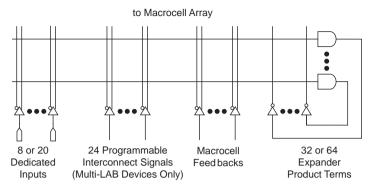

### **Expander Product Terms**

While most logic functions can be implemented with the product terms available in each macrocell, some logic functions are more complex and require additional product terms. Although additional macrocells can be used to supply the needed logic resources, the MAX 5000 architecture can also use shared expander product terms that provide additional product terms directly to any macrocell in the same LAB. These expanders help ensure that logic is synthesized with the fewest possible logic resources to obtain the fastest possible speed.

Each LAB has 32 shared expanders (except for EPM5032 devices, which have 64). The expanders can be viewed as a pool of uncommitted product terms. The expander product-term array (see Figure 3) contains unallocated, inverted product terms that feed the macrocell array. Expanders can be used and shared by all product terms in the LAB. Wherever extra logic is needed (including register control functions), expanders can be used to implement the logic. These expanders provide the flexibility to implement register- and product-term-intensive designs in MAX 5000 EPLDs.

Figure 3. Expander Product Terms

Expanders are fed by all signals in the LAB. One expander can feed all macrocells in the LAB or multiple product terms in the same macrocell. Since expanders also feed the secondary product terms of each macrocell, complex logic functions can be implemented without using additional macrocells. A small delay ( $t_{SEXP}$ ) is incurred when shared expanders are used.

## **Programmable Interconnect Array**

The multi-LAB MAX 5000 devices—EPM5064, EPM5128, EPM5130, and EPM5192 devices—use a programmable interconnect array (PIA) to route signals between the various LABs. The PIA, which is fed by all macrocell and I/O pin feedbacks, routes only the signals required for implementing logic in an LAB. While the routing delays of segmented routing schemes in masked or field-programmable gate arrays (FPGAs) are cumulative, variable, and path-dependent, the MAX 5000 PIA has a fixed delay. The PIA thus eliminates skew between signals and makes timing performance easy to predict.

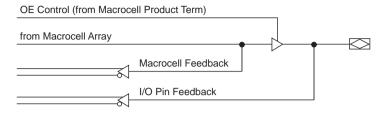

#### I/O Control Blocks

Each LAB has an I/O control block that allows each I/O pin to be individually configured for input, output, or bidirectional operation. See Figure 4. The I/O control block is fed by the macrocell array. A dedicated macrocell product term controls a tri-state buffer, which drives the I/O pin.

Figure 4. I/O Control Block

The MAX 5000 architecture provides dual I/O feedback in which macrocell and I/O pin feedbacks are independent, allowing maximum flexibility. When an I/O pin is configured as an input, the associated macrocell can be used for buried logic. Using an I/O pin as an input in single-LAB devices reduces the number of available expanders by two. In multi-LAB devices, I/O pins feed the PIA directly.

# **Design Security**

All MAX 5000 EPLDs contain a programmable security bit that controls access to the data programmed into the device. When this bit is programmed, a proprietary design implemented in the device cannot be copied or retrieved. This feature provides a high level of design security, because programmed data within EPROM cells is invisible. The security bit that controls this function, as well as all other program data, is reset only when the device is erased.

## Generic Testing

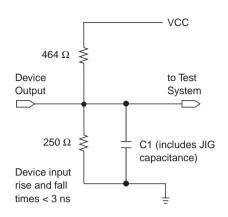

MAX 5000 EPLDs are fully functionally tested. Complete testing of each programmable EPROM bit and all internal logic elements ensures 100% programming yield. Test patterns can be used and then erased during early stages of the device production flow. The devices also contain on-board logic test circuitry to allow verification of function and AC specifications during the production flow. AC test measurements are taken under conditions equivalent to those in Figure 5.

Figure 5. AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast ground-current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result.

# Device Programming

All MAX 5000 EPLDs can be programmed on 486- and Pentium-based PCs with the MAX+PLUS II Programmer, an Altera Logic Programmer card, the Master Programming Unit (MPU), and the appropriate device adapter. The MPU checks continuity to ensure adequate electrical contact between the adapter and the device.

For more information, see the *Altera Programming Hardware Data Sheet* in this data book.

MAX+PLUS II software can use text- or waveform-format test vectors created with the MAX+PLUS II Text Editor or Waveform Editor to test a programmed device. For added design verification, designers can perform functional testing to compare the functional behavior of a MAX 5000 EPLD with the simulation results. This feature requires a device adapter with the "PLM-" prefix.

Data I/O, BP Microsystems, and other programming hardware manufacturers also offer programming support for Altera devices.

For more information, see *Programming Hardware Manufacturers* in this data book.

# QFP Carrier & Development Socket

MAX 5000 devices in 100-pin QFP packages are shipped in special plastic carriers to protect the QFP leads. Each carrier can be used with a prototype development socket and programming hardware available from Altera or third-party programming manufacturers such as Data I/O and BP Microsystems. This carrier technology makes it possible to program, test, erase, and reprogram devices without exposing the leads to mechanical stress.

For detailed information and carrier dimensions, refer to the *QFP Carrier* & *Development Socket Data Sheet* and *Application Note 71 (Guidelines for Handling J-Lead & QFP Devices)* in this data book.

# Operating Conditions

The following tables provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for MAX 5000 devices.

### MAX 5000 Device Absolute Maximum Ratings Note (1)

| Symbol           | Parameter                  | Conditions                       | Min  | Max | Unit |

|------------------|----------------------------|----------------------------------|------|-----|------|

| V <sub>CC</sub>  | Supply voltage             | With respect to ground, Note (2) | -2.0 | 7.0 | V    |

| VI               | DC input voltage           |                                  | -2.0 | 7.0 | V    |

| I <sub>OUT</sub> | DC output current, per pin |                                  | -25  | 25  | mA   |

| T <sub>STG</sub> | Storage temperature        | No bias                          | -65  | 135 | °C   |

| T <sub>AMB</sub> | Ambient temperature        | Under bias                       | -65  | 135 | °C   |

| TJ               | Junction temperature       | Ceramic packages, under bias     |      | 150 | °C   |

|                  |                            | Plastic packages, under bias     |      | 135 | °C   |

### MAX 5000 Device Recommended Operating Conditions

| Symbol          | Parameter           | Conditions         | Min        | Max             | Unit |

|-----------------|---------------------|--------------------|------------|-----------------|------|

| V <sub>CC</sub> | Supply voltage      | Notes (3), (4)     | 4.75 (4.5) | 5.25 (5.5)      | V    |

| VI              | Input voltage       |                    | 0          | V <sub>CC</sub> | V    |

| Vo              | Output voltage      |                    | 0          | V <sub>CC</sub> | V    |

| T <sub>A</sub>  | Ambient temperature | For commercial use | 0          | 70              | °C   |

|                 |                     | For industrial use | -40        | 85              | °C   |

| t <sub>R</sub>  | Input rise time     |                    |            | 100             | ns   |

| t <sub>F</sub>  | Input fall time     |                    |            | 100             | ns   |

### MAX 5000 Device DC Operating Conditions Note (5)

| Symbol          | Parameter                                  | Conditions                                  | Min  | Тур | Max                   | Unit |

|-----------------|--------------------------------------------|---------------------------------------------|------|-----|-----------------------|------|

| V <sub>IH</sub> | High-level input voltage                   |                                             | 2.0  |     | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> | Low-level input voltage                    |                                             | -0.3 |     | 0.8                   | V    |

| V <sub>OH</sub> | High-level TTL output voltage              | I <sub>OH</sub> = -4 mA DC, <i>Note (6)</i> | 2.4  |     |                       | V    |

| V <sub>OL</sub> | Low-level output voltage                   | I <sub>OL</sub> = 8 mA DC, Note (6)         |      |     | 0.45                  | V    |

| I <sub>I</sub>  | Leakage current of dedicated inputs        | $V_I = V_{CC}$ or ground                    | -10  |     | 10                    | μΑ   |

| I <sub>OZ</sub> | I/O pin tri-state output off-state current | $V_O = V_{CC}$ or ground                    | -40  |     | 40                    | μΑ   |

#### EPM5032 MAX 5000 Device Capacitance

| Symbol           | Parameter             | Conditions                          | Min | Max | Unit |

|------------------|-----------------------|-------------------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input pin capacitance | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |

| C <sub>I/O</sub> | I/O pin capacitance   | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 12  | pF   |

#### EPM5064, EPM5128, EPM5130 & EPM5192 MAX 5000 Device Capacitance

| Symbol           | Parameter             | Conditions                          | Min | Max | Unit |

|------------------|-----------------------|-------------------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input pin capacitance | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |

| C <sub>I/O</sub> | I/O pin capacitance   | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 20  | pF   |

#### Notes to tables:

- (1) See Operating Requirements for Altera Devices Data Sheet in this data book.

- (2) Minimum DC input is -0.3 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 7.0 V for periods shorter than 20 ns under no-load conditions.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time for MAX 5000 devices is 10 ms.

- (5) Typical values are for  $T_A = 25^{\circ}$  C and  $V_{CC} = 5.0$  V.

- (6) The I<sub>OH</sub> parameter refers to high-level TTL output current; the I<sub>OL</sub> parameter refers to low-level TTL output current.

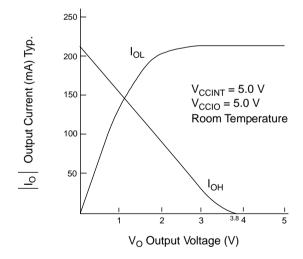

Figure 6 shows typical output drive characteristics of MAX 5000 devices.

Figure 6. Output Drive Characteristics of MAX 5000 Devices

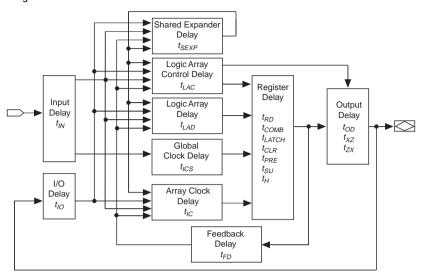

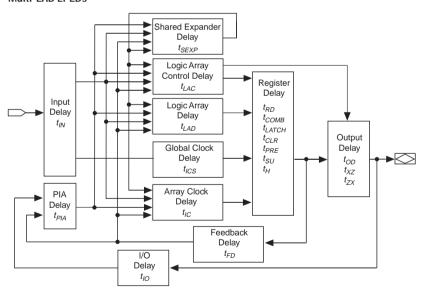

# Timing Model

MAX 5000 EPLD timing can be analyzed with the MAX+PLUS II software, with a variety of other industry-standard EDA simulators and timing analyzers, or with the timing model shown in Figure 7. MAX 5000 EPLDs have fixed internal delays that allow the designer to determine the worst-case timing for any design. The MAX+PLUS II software provides timing simulation, point-to-point delay prediction, and detailed timing analysis for system-level performance evaluation.

Figure 7. MAX 5000 Timing Model

#### Single-LAB EPLDs

#### Multi-LAB EPLDs

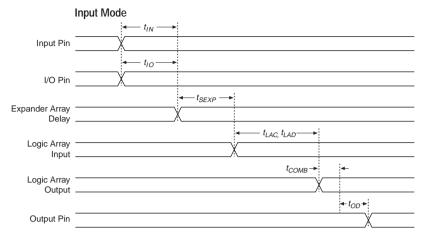

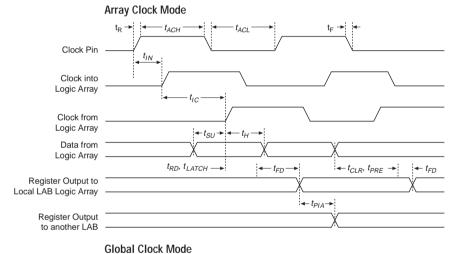

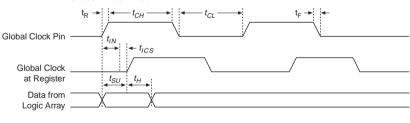

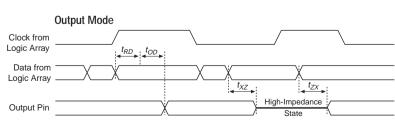

Timing information can be derived from the timing model and parameters for a particular EPLD. External timing parameters are calculated with the sum of internal parameters and represent pin-to-pin timing delays. Figure 8 shows the internal timing relationship for internal and external delay parameters.

For more information on EPLD timing, refer to *Application Note 78* (*Understanding MAX 5000 & Classic Timing*) in this data book.

### Figure 8. Switching Waveforms

In multi-LAB EPLDs, I/O pins that are used as inputs traverse the PIA.

$t_R$  and  $t_F < 3$  ns. Inputs are driven at 3 V for a logic high and 0 V for a logic low. All timing characteristics are measured at 1.5 V.

## EPM5032 AC Operating Conditions Note (1)

| External          | Timing Parameters                       |                | EPM50 | )32-15 | EPM5032-20 |     | EPM5032-25 |     |      |

|-------------------|-----------------------------------------|----------------|-------|--------|------------|-----|------------|-----|------|

| Symbol            | Parameter                               | Conditions     | Min   | Max    | Min        | Max | Min        | Max | Unit |

| t <sub>PD1</sub>  | Input to non-registered output          | C1 = 35 pF     |       | 15     |            | 20  |            | 25  | ns   |

| t <sub>PD2</sub>  | I/O input to non-registered output      | C1 = 35 pF     |       | 15     |            | 20  |            | 25  | ns   |

| t <sub>SU</sub>   | Global clock setup time                 |                | 9     |        | 12         |     | 15         |     | ns   |

| t <sub>H</sub>    | Global clock hold time                  |                | 0     |        | 0          |     | 0          |     | ns   |

| t <sub>CO1</sub>  | Global clock to output delay            | C1 = 35 pF     |       | 10     |            | 12  |            | 15  | ns   |

| t <sub>CH</sub>   | Global clock high time                  |                | 6     |        | 7          |     | 8          |     | ns   |

| t <sub>CL</sub>   | Global clock low time                   |                | 6     |        | 7          |     | 8          |     | ns   |

| t <sub>ASU</sub>  | Array clock setup time                  |                | 5     |        | 6          |     | 8          |     | ns   |

| t <sub>AH</sub>   | Array clock hold time                   |                | 5     |        | 6          |     | 8          |     | ns   |

| t <sub>ACO1</sub> | Array clock to output delay             | C1 = 35 pF     |       | 15     |            | 18  |            | 22  | ns   |

| t <sub>ACH</sub>  | Array clock high time                   | Note (2)       | 6     |        | 7          |     | 9          |     | ns   |

| t <sub>ACL</sub>  | Array clock low time                    |                | 7     |        | 9          |     | 11         |     | ns   |

| t <sub>ODH</sub>  | Output data hold time after clock       | C1 = 35 pF (3) | 1     |        | 1          |     | 1          |     | ns   |

| t <sub>CNT</sub>  | Minimum global clock period             |                |       | 13     |            | 16  |            | 20  | ns   |

| f <sub>CNT</sub>  | Maximum internal global clock frequency | Note (4)       | 76.9  |        | 62.5       |     | 50         |     | MHz  |

| t <sub>ACNT</sub> | Minimum array clock period              |                |       | 13     |            | 16  |            | 20  | ns   |

| f <sub>ACNT</sub> | Maximum internal array clock frequency  | Note (4)       | 76.9  |        | 62.5       |     | 50         |     | MHz  |

| f <sub>MAX</sub>  | Maximum clock frequency                 | Note (5)       | 83.3  |        | 71.4       |     | 62.5       |     | MHz  |

| Internal           | Timing Parameters Note (6)     |            | EPM50 | 032-15 | EPM50 | 032-20 | EPM5032-25 |     |      |

|--------------------|--------------------------------|------------|-------|--------|-------|--------|------------|-----|------|

| Symbol             | Parameter                      | Conditions | Min   | Max    | Min   | Max    | Min        | Max | Unit |

| t <sub>IN</sub>    | Input pad and buffer delay     |            |       | 3      |       | 5      |            | 7   | ns   |

| t <sub>IO</sub>    | I/O input pad and buffer delay |            |       | 3      |       | 5      |            | 7   | ns   |

| t <sub>SEXP</sub>  | Expander array delay           |            |       | 8      |       | 10     |            | 15  | ns   |

| t <sub>LAD</sub>   | Logic array delay              |            |       | 7      |       | 10     |            | 13  | ns   |

| t <sub>LAC</sub>   | Logic control array delay      |            |       | 4      |       | 4      |            | 4   | ns   |

| t <sub>OD</sub>    | Output buffer and pad delay    | C1 = 35 pF |       | 4      |       | 4      |            | 4   | ns   |

| t <sub>ZX</sub>    | Output buffer enable delay     | C1 = 35 pF |       | 7      |       | 7      |            | 7   | ns   |

| t <sub>XZ</sub>    | Output buffer disable delay    | C1 = 5 pF  |       | 7      |       | 7      |            | 7   | ns   |

| t <sub>SU</sub>    | Register setup time            |            | 4     |        | 4     |        | 5          |     | ns   |

| t <sub>LATCH</sub> | Flow-through latch delay       |            |       | 1      |       | 1      |            | 1   | ns   |

| t <sub>RD</sub>    | Register delay                 |            |       | 1      |       | 1      |            | 1   | ns   |

| t <sub>COMB</sub>  | Combinatorial delay            |            |       | 1      |       | 1      |            | 1   | ns   |

| t <sub>H</sub>     | Register hold time             |            | 5     |        | 8     |        | 10         |     | ns   |

| t <sub>IC</sub>    | Array clock delay              |            |       | 7      |       | 8      |            | 10  | ns   |

| t <sub>ICS</sub>   | Global clock delay             |            |       | 2      |       | 2      |            | 3   | ns   |

| t <sub>FD</sub>    | Feedback delay                 |            |       | 1      |       | 1      |            | 1   | ns   |

| t <sub>PRE</sub>   | Register preset time           |            |       | 5      |       | 6      |            | 9   | ns   |

| t <sub>CLR</sub>   | Register clear time            |            |       | 5      |       | 6      |            | 9   | ns   |

## EPM5064, EPM5128, EPM5130 & EPM5192 AC Operating Conditions Note (1)

| External          | Timing Parameters                       |                             | EPM5<br>EPM5 | EPM5064-1<br>EPM5128-1<br>EPM5130-1<br>EPM5192-1 |     | 064-2<br>128-2 | EPM5064<br>EPM5128<br>EPM5130<br>EPM5192 |     |      |

|-------------------|-----------------------------------------|-----------------------------|--------------|--------------------------------------------------|-----|----------------|------------------------------------------|-----|------|

| Symbol            | Parameter                               | Conditions                  | Min          | Max                                              | Min | Max            | Min                                      | Max | Unit |

| t <sub>PD1</sub>  | Input to non-registered output          | C1 = 35 pF                  |              | 25                                               |     | 30             |                                          | 35  | ns   |

| t <sub>PD2</sub>  | I/O input to non-registered output      | C1 = 35 pF                  |              | 40                                               |     | 45             |                                          | 55  | ns   |

| t <sub>SU</sub>   | Global clock setup time                 |                             | 15           |                                                  | 20  |                | 25                                       |     | ns   |

| t <sub>H</sub>    | Global clock hold time                  |                             | 0            |                                                  | 0   |                | 0                                        |     | ns   |

| t <sub>CO1</sub>  | Global clock to output delay            | C1 = 35 pF                  |              | 14                                               |     | 16             |                                          | 20  | ns   |

| t <sub>CH</sub>   | Global clock high time                  |                             | 8            |                                                  | 10  |                | 12.5                                     |     | ns   |

| t <sub>CL</sub>   | Global clock low time                   |                             | 8            |                                                  | 10  |                | 12.5                                     |     | ns   |

| t <sub>ASU</sub>  | Array clock setup time                  |                             | 5            |                                                  | 6   |                | 10                                       |     | ns   |

| t <sub>AH</sub>   | Array clock hold time                   |                             | 6            |                                                  | 8   |                | 10                                       |     | ns   |

| t <sub>ACO1</sub> | Array clock to output delay             | C1 = 35 pF                  |              | 25                                               |     | 30             |                                          | 35  | ns   |

| t <sub>ACH</sub>  | Array clock high time                   | Note (2)                    | 11           |                                                  | 14  |                | 16                                       |     | ns   |

| t <sub>ACL</sub>  | Array clock low time                    |                             | 9            |                                                  | 11  |                | 14                                       |     | ns   |

| t <sub>CNT</sub>  | Minimum global clock period             |                             |              | 20                                               |     | 25             |                                          | 30  | ns   |

| t <sub>ODH</sub>  | Output data hold time after clock       | C1 = 35 pF, <i>Note (3)</i> | 2            |                                                  | 2   |                | 2                                        |     | ns   |

| f <sub>CNT</sub>  | Maximum internal global clock frequency | Note (4)                    | 50           |                                                  | 40  |                | 33.3                                     |     | MHz  |

| tACNT             | Minimum array clock period              |                             |              | 20                                               |     | 25             |                                          | 30  | ns   |

| f <sub>ACNT</sub> | Maximum internal array clock frequency  | Note (4)                    | 50           |                                                  | 40  |                | 33.3                                     |     | MHz  |

| f <sub>MAX</sub>  | Maximum clock frequency                 | Note (5)                    | 62.5         |                                                  | 50  |                | 40                                       |     | MHz  |

| Internal           | Internal Timing Parameters Note (6)   |            | EPM5 | 064-1<br>128-1<br>130-1<br>192-1 | EPM5064-2<br>EPM5128-2 |     | EPM5064<br>EPM5128<br>EPM5130<br>EPM5192 |     |      |

|--------------------|---------------------------------------|------------|------|----------------------------------|------------------------|-----|------------------------------------------|-----|------|

| Symbol             | Parameter                             | Conditions | Min  | Max                              | Min                    | Max | Min                                      | Max | Unit |

| t <sub>IN</sub>    | Input pad and buffer delay            |            |      | 5                                |                        | 7   |                                          | 11  | ns   |

| t <sub>IO</sub>    | I/O input pad and buffer delay        |            |      | 6                                |                        | 6   |                                          | 11  | ns   |

| t <sub>SEXP</sub>  | Expander array delay                  |            |      | 12                               |                        | 14  |                                          | 20  | ns   |

| t <sub>LAD</sub>   | Logic array delay                     |            |      | 12                               |                        | 14  |                                          | 14  | ns   |

| t <sub>LAC</sub>   | Logic control array delay             |            |      | 10                               |                        | 12  |                                          | 13  | ns   |

| $t_{OD}$           | Output buffer and pad delay           | C1 = 35 pF |      | 5                                |                        | 5   |                                          | 6   | ns   |

| $t_{ZX}$           | Output buffer enable delay            | C1 = 35 pF |      | 10                               |                        | 11  |                                          | 13  | ns   |

| $t_{XZ}$           | Output buffer disable delay           | C1 = 5 pF  |      | 10                               |                        | 11  |                                          | 13  | ns   |

| $t_{SU}$           | Register setup time                   |            | 6    |                                  | 8                      |     | 12                                       |     | ns   |

| t <sub>LATCH</sub> | Flow-through latch delay              |            |      | 3                                |                        | 4   |                                          | 4   | ns   |

| $t_{RD}$           | Register delay                        |            |      | 1                                |                        | 2   |                                          | 2   | ns   |

| t <sub>COMB</sub>  | Combinatorial delay                   |            |      | 3                                |                        | 4   |                                          | 4   | ns   |

| $t_H$              | Register hold time                    |            | 4    |                                  | 6                      |     | 8                                        |     | ns   |

| t <sub>IC</sub>    | Array clock delay                     |            |      | 14                               |                        | 16  |                                          | 16  | ns   |

| t <sub>ICS</sub>   | Global clock delay                    |            |      | 3                                |                        | 2   |                                          | 1   | ns   |

| $t_{FD}$           | Feedback delay                        |            |      | 1                                |                        | 1   |                                          | 2   | ns   |

| t <sub>PRE</sub>   | Register preset time                  |            |      | 5                                |                        | 6   |                                          | 7   | ns   |

| t <sub>CLR</sub>   | Register clear time                   |            |      | 5                                |                        | 6   |                                          | 7   | ns   |

| t <sub>PIA</sub>   | Programmable interconnect array delay |            |      | 14                               |                        | 16  |                                          | 20  | ns   |

#### Notes to tables:

- (1) Operating conditions are specified in the "MAX 5000 Device Recommended Operating Conditions" on page 395.

- (2) This parameter is measured with a positive-edge-triggered clock at the register. For negative-edge clocking, the t<sub>ACH</sub> and t<sub>ACL</sub> parameters must be swapped.

- (3) This parameter is a guideline that is sample-tested only. It is based on extensive device characterization and applies to both global and array clocking.

- (4) For EPM5032 devices, this parameter is measured with a 32-bit counter programmed into the device. For EPM5064, EPM5128, EPM5130, and EPM5192 devices, this parameter is measured with a 16-bit counter programmed into each LAB.  $I_{CC}$  is characterized at  $0^{\circ}$  C.

- (5) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

- (6) For information on internal timing parameters, refer to *Application Note 78 (Understanding MAX 5000 & Classic Timing)* in this data book.

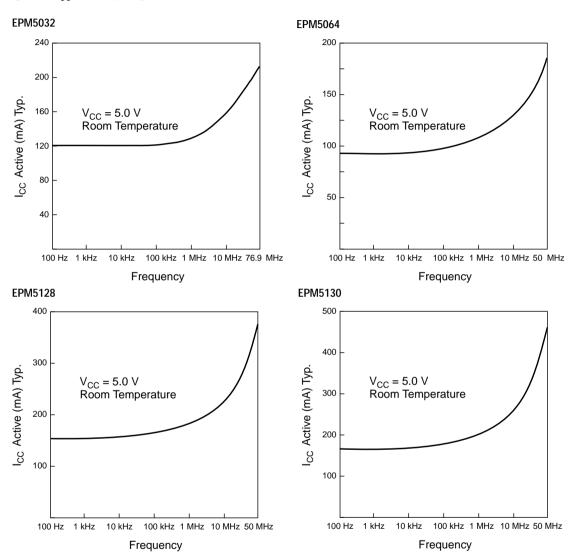

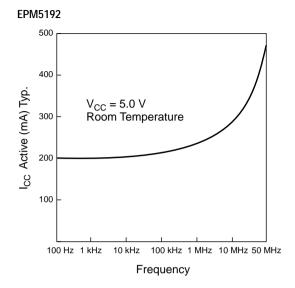

Figure 9 shows the typical supply current versus frequency of MAX 5000 devices.

Figure 9. I<sub>CC</sub> vs. Frequency for MAX 5000 Devices (Part 1 of 2)

Figure 9. I<sub>CC</sub> vs. Frequency for MAX 5000 Devices (Part 2 of 2)

# Device Pin-Outs

Tables 4 through 13 show the pin names and numbers for the pins in each MAX 5000 device package.

| Table 4. EPM5032 Dedicated Pin-Outs |                         |                           |  |  |  |  |  |  |

|-------------------------------------|-------------------------|---------------------------|--|--|--|--|--|--|

| Pin Name                            | 28-Pin J-Lead           | 28-Pin DIP                |  |  |  |  |  |  |

| INPUT/CLK                           | 9                       | 2                         |  |  |  |  |  |  |

| INPUT                               | 6, 7, 8, 20, 21, 22, 23 | 1, 13, 14, 15, 16, 27, 28 |  |  |  |  |  |  |

| GND                                 | 15, 28                  | 8, 21                     |  |  |  |  |  |  |

| VCC                                 | 1, 14                   | 7, 22                     |  |  |  |  |  |  |

| Table 5. | Table 5. EPM5032 I/O Pin-Outs |               |    |                  |               |  |  |  |  |  |  |

|----------|-------------------------------|---------------|----|------------------|---------------|--|--|--|--|--|--|

| MC       | 28-Pin<br>J-Lead              | 28-Pin<br>DIP | MC | 28-Pin<br>J-Lead | 28-Pin<br>DIP |  |  |  |  |  |  |

| 1        | 10                            | 3             | 17 | 24               | 17            |  |  |  |  |  |  |

| 2        | _                             | _             | 18 | _                | _             |  |  |  |  |  |  |

| 3        | 11                            | 4             | 19 | 25               | 18            |  |  |  |  |  |  |

| 4        | _                             | _             | 20 | _                | _             |  |  |  |  |  |  |

| 5        | 12                            | 5             | 21 | 26               | 19            |  |  |  |  |  |  |

| 6        | _                             | _             | 22 | _                | _             |  |  |  |  |  |  |

| 7        | 13                            | 6             | 23 | 27               | 20            |  |  |  |  |  |  |

| 8        | _                             | _             | 24 | _                | _             |  |  |  |  |  |  |

| 9        | 16                            | 9             | 25 | 2                | 23            |  |  |  |  |  |  |

| 10       | _                             | _             | 26 | _                | _             |  |  |  |  |  |  |

| 11       | 17                            | 10            | 27 | 3                | 24            |  |  |  |  |  |  |

| 12       | _                             | _             | 28 | _                | _             |  |  |  |  |  |  |

| 13       | 18                            | 11            | 29 | 4                | 25            |  |  |  |  |  |  |

| 14       | _                             | -             | 30 | _                | _             |  |  |  |  |  |  |

| 15       | 19                            | 12            | 31 | 5                | 26            |  |  |  |  |  |  |

| 16       | _                             | _             | 32 | _                | _             |  |  |  |  |  |  |

| Table 6. EPM5064 Dedicated Pin-Outs |                           |  |  |  |  |  |

|-------------------------------------|---------------------------|--|--|--|--|--|

| Pin Name 44-Pin J-Lead              |                           |  |  |  |  |  |

| INPUT/CLK                           | 34                        |  |  |  |  |  |

| INPUT                               | 9, 11, 12, 13, 31, 33, 35 |  |  |  |  |  |

| GND                                 | 10, 21, 32, 43            |  |  |  |  |  |

| VCC                                 | 3, 14, 25, 36             |  |  |  |  |  |

| Table 7. EP | PM5064 I/O P | in-Outs (Part    | 1 of 2) |     |                  |

|-------------|--------------|------------------|---------|-----|------------------|

| MC          | LAB          | 44-Pin<br>J-Lead | MC      | LAB | 44-Pin<br>J-Lead |

| 1           | Α            | 2                | 17      | В   | 15               |

| 2           | Α            | 4                | 18      | В   | 16               |

| 3           | Α            | 5                | 19      | В   | 17               |

| 4           | Α            | 6                | 20      | В   | 18               |

| 5           | Α            | 7                | 21      | В   | 19               |

| 6           | Α            | 8                | 22      | В   | 20               |

| 7           | Α            | _                | 23      | В   | 22               |

| 8           | Α            | _                | 24      | В   | 23               |

| 9           | Α            | _                | 25      | В   | _                |

| 10          | Α            | _                | 26      | В   | _                |

| 11          | Α            | _                | 27      | В   | _                |

| 12          | Α            | _                | 28      | В   | _                |

| 13          | Α            | _                | 29      | В   | _                |

| 14          | Α            | _                | 30      | В   | _                |

| 15          | Α            | _                | 31      | В   | _                |

| 16          | Α            | _                | 32      | В   | _                |

| MC | LAB | 44-Pin<br>J-Lead | MC | LAB | 44-Pin<br>J-Lead |

|----|-----|------------------|----|-----|------------------|

| 33 | С   | 24               | 49 | D   | 37               |

| 34 | С   | 26               | 50 | D   | 38               |

| 35 | С   | 27               | 51 | D   | 39               |

| 36 | С   | 28               | 52 | D   | 40               |

| 37 | С   | 29               | 53 | D   | 41               |

| 38 | С   | 30               | 54 | D   | 42               |

| 39 | С   | _                | 55 | D   | 44               |

| 40 | С   | _                | 56 | D   | 1                |

| 41 | С   | _                | 57 | D   | _                |

| 42 | С   | _                | 58 | D   | _                |

| 43 | С   | _                | 59 | D   | _                |

| 44 | С   | _                | 60 | D   | _                |

| 45 | С   | _                | 61 | D   | _                |

| 46 | С   | _                | 62 | D   | _                |

| 47 | С   | _                | 63 | D   | _                |

| 48 | С   | _                | 64 | D   | _                |

| Table 8. EPM5128 Dedicated Pin-Outs |                           |                            |  |  |  |  |  |  |  |

|-------------------------------------|---------------------------|----------------------------|--|--|--|--|--|--|--|

| Pin Name                            | 68-Pin J-Lead             | 68-Pin PGA                 |  |  |  |  |  |  |  |

| INPUT/CLK                           | 1                         | B6                         |  |  |  |  |  |  |  |

| INPUT                               | 2, 32, 34, 35, 36, 66, 68 | A6, L4, L5, L6, K6, A8, A7 |  |  |  |  |  |  |  |

| GND                                 | 16, 33, 50, 67            | B7, E2, G10, K5            |  |  |  |  |  |  |  |

| VCC                                 | 3, 20, 37, 54             | B5, E10, G2, K7            |  |  |  |  |  |  |  |

| Table 9. EPM5128 I/O Pin-Outs (Part 1 of 3) |     |                  |               |    |     |                  |               |  |  |  |

|---------------------------------------------|-----|------------------|---------------|----|-----|------------------|---------------|--|--|--|

| MC                                          | LAB | 68-Pin<br>J-Lead | 68-Pin<br>PGA | MC | LAB | 68-Pin<br>J-Lead | 68-Pin<br>PGA |  |  |  |

| 1                                           | Α   | 4                | A5            | 17 | В   | 12               | C2            |  |  |  |

| 2                                           | Α   | 5                | B4            | 18 | В   | 13               | C1            |  |  |  |

| 3                                           | Α   | 6                | A4            | 19 | В   | 14               | D2            |  |  |  |

| 4                                           | Α   | 7                | В3            | 20 | В   | 15               | D1            |  |  |  |

| 5                                           | Α   | 8                | А3            | 21 | В   | 17               | E1            |  |  |  |

| 6                                           | Α   | 9                | A2            | 22 | В   | _                | -             |  |  |  |

| 7                                           | Α   | 10               | B2            | 23 | В   | _                | -             |  |  |  |

| 8                                           | Α   | 11               | B1            | 24 | В   | _                | -             |  |  |  |

| 9                                           | Α   | _                | _             | 25 | В   | _                | -             |  |  |  |

| 10                                          | Α   | _                | _             | 26 | В   | _                | -             |  |  |  |

| 11                                          | Α   | _                | _             | 27 | В   | _                | -             |  |  |  |

| 12                                          | Α   | _                | _             | 28 | В   | _                | -             |  |  |  |

| 13                                          | Α   | _                | _             | 29 | В   | _                | -             |  |  |  |

| 14                                          | Α   | _                | _             | 30 | В   | _                | -             |  |  |  |

| 15                                          | Α   | _                | _             | 31 | В   | _                | -             |  |  |  |

| 16                                          | Α   | _                | _             | 32 | В   | _                | -             |  |  |  |

| MC | LAB | 68-Pin<br>J-Lead | 68-Pin<br>PGA | MC | LAB | 68-Pin<br>J-Lead | 68-Pin<br>PGA |

|----|-----|------------------|---------------|----|-----|------------------|---------------|

| 33 | С   | 18               | F2            | 49 | D   | 24               | J2            |

| 34 | С   | 19               | F1            | 50 | D   | 25               | J1            |

| 35 | С   | 21               | G1            | 51 | D   | 26               | K1            |

| 36 | С   | 22               | H2            | 52 | D   | 27               | K2            |

| 37 | С   | 23               | H1            | 53 | D   | 28               | L2            |

| 38 | С   | _                | _             | 54 | D   | 29               | K3            |

| 39 | С   | _                | _             | 55 | D   | 30               | L3            |

| 40 | С   | _                | _             | 56 | D   | 31               | K4            |

| 41 | С   | _                | _             | 57 | D   | _                | _             |

| 42 | С   | _                | _             | 58 | D   | _                | _             |

| 43 | С   | _                | _             | 59 | D   | _                | _             |

| 44 | С   | _                | _             | 60 | D   | _                | _             |

| 45 | С   | _                | _             | 61 | D   | _                | _             |

| 46 | С   | _                | _             | 62 | D   | _                | _             |

| 47 | С   | _                | _             | 63 | D   | _                | _             |

| 48 | С   | _                | _             | 64 | D   | _                | _             |

| 65 | Е   | 38               | L7            | 81 | F   | 46               | J10           |

| 66 | Е   | 39               | K8            | 82 | F   | 47               | J11           |

| 67 | Е   | 40               | L8            | 83 | F   | 48               | H10           |

| 68 | E   | 41               | K9            | 84 | F   | 49               | H11           |

| 69 | E   | 42               | L9            | 85 | F   | 51               | G11           |

| 70 | Е   | 43               | L10           | 86 | F   | _                | _             |

| 71 | E   | 44               | K10           | 87 | F   | _                | _             |

| 72 | E   | 45               | K11           | 88 | F   | _                | _             |

| 73 | E   | _                | _             | 89 | F   | _                | _             |

| 74 | E   | _                | _             | 90 | F   | _                | _             |

| 75 | Е   | _                | _             | 91 | F   | _                | _             |

| 76 | E   | _                | _             | 92 | F   | _                | _             |

| 77 | E   | _                | _             | 93 | F   | _                | _             |

| 78 | E   | _                | _             | 94 | F   | _                | _             |

| 79 | Е   | _                | _             | 95 | F   | _                | _             |

| 80 | Е   | _                | _             | 96 | F   | _                | _             |

| Table 9. EPM5128 I/O Pin-Outs (Part 3 of 3) |     |                  |               |     |     |                  |               |  |  |  |

|---------------------------------------------|-----|------------------|---------------|-----|-----|------------------|---------------|--|--|--|

| MC                                          | LAB | 68-Pin<br>J-Lead | 68-Pin<br>PGA | MC  | LAB | 68-Pin<br>J-Lead | 68-Pin<br>PGA |  |  |  |

| 97                                          | G   | 52               | F10           | 113 | Н   | 58               | C10           |  |  |  |

| 98                                          | G   | 53               | F11           | 114 | Н   | 59               | C11           |  |  |  |

| 99                                          | G   | 55               | E11           | 115 | Н   | 60               | B11           |  |  |  |

| 100                                         | G   | 56               | D10           | 116 | Н   | 61               | B10           |  |  |  |

| 101                                         | G   | 57               | D11           | 117 | Н   | 62               | A10           |  |  |  |

| 102                                         | G   | _                | -             | 118 | Н   | 63               | В9            |  |  |  |

| 103                                         | G   | _                | -             | 119 | Н   | 64               | A9            |  |  |  |

| 104                                         | G   | _                | _             | 120 | Н   | 65               | B8            |  |  |  |

| 105                                         | G   | _                | -             | 121 | Н   | _                | -             |  |  |  |

| 106                                         | G   | _                | -             | 122 | Н   | _                | -             |  |  |  |

| 107                                         | G   | _                | _             | 123 | Н   | _                | -             |  |  |  |

| 108                                         | G   | _                | -             | 124 | Н   | _                | -             |  |  |  |

| 109                                         | G   | _                | -             | 125 | Н   | _                | -             |  |  |  |

| 110                                         | G   | _                | -             | 126 | Н   | _                | -             |  |  |  |

| 111                                         | G   | _                | -             | 127 | Н   | _                | -             |  |  |  |

| 112                                         | G   | _                | _             | 128 | Н   | _                | _             |  |  |  |

| Table 10. EPM5130 Dedicated Pin-Outs |                                                                                 |                                                                                         |                                                                                        |  |  |  |  |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Pin Name                             | 84-Pin J-Lead                                                                   | 100-Pin PGA                                                                             | 100-Pin PQFP                                                                           |  |  |  |  |  |  |  |  |

| INPUT/CLK                            | 1                                                                               | C7                                                                                      | 16                                                                                     |  |  |  |  |  |  |  |  |

| INPUT                                | 2, 5, 6, 7, 36, 37,<br>38, 41, 42, 43, 44,<br>47, 48, 49, 78, 79,<br>80, 83, 84 | A5, A7, A8, A9,<br>A10, B5, B7, B9,<br>C6, L7, L8, M5,<br>M7, M9, N4, N5,<br>N6, N7, N9 | 9, 10, 11, 14, 15,<br>16, 17, 20, 21, 22,<br>59, 60, 61, 64, 65,<br>66, 67, 70, 71, 72 |  |  |  |  |  |  |  |  |

| GND                                  | 19, 20, 39, 40, 61,<br>62, 81, 82                                               | B8, C8, F2, F3,<br>H11, H12, L6, M6                                                     | 12, 13, 37, 38, 62,<br>63, 87, 88                                                      |  |  |  |  |  |  |  |  |

| VCC                                  | 3, 4, 23, 24, 45, 46,<br>65, 66                                                 | A6, B6, F12, F13,<br>H1, H2, M8, N8                                                     | 18, 19, 43, 44, 68,<br>69, 93, 94                                                      |  |  |  |  |  |  |  |  |

| Table 11. EPM5130 I/O Pin-Outs (Part 1 of 2) |     |                  |                |                 |    |     |                  |                |                 |

|----------------------------------------------|-----|------------------|----------------|-----------------|----|-----|------------------|----------------|-----------------|

| MC                                           | LAB | 84-Pin<br>J-Lead | 100-Pin<br>PGA | 100-Pin<br>PQFP | МС | LAB | 84-Pin<br>J-Lead | 100-Pin<br>PGA | 100-Pin<br>PQFP |

| 1                                            | Α   | 8                | B13            | 1               | 17 | В   | 14               | A4             | 23              |

| 2                                            | Α   | 9                | C12            | 2               | 18 | В   | 15               | B4             | 24              |

| 3                                            | Α   | 10               | A13            | 3               | 19 | В   | 16               | А3             | 25              |

| 4                                            | Α   | 11               | B12            | 4               | 20 | В   | 17               | A2             | 26              |

| 5                                            | Α   | 12               | A12            | 5               | 21 | В   | 18               | В3             | 27              |

| 6                                            | Α   | 13               | B11            | 6               | 22 | В   | 21               | A1             | 28              |

| 7                                            | Α   | _                | A11            | 7               | 23 | В   | _                | B2             | 29              |

| 8                                            | Α   | _                | B10            | 8               | 24 | В   | _                | B1             | 30              |

| 9                                            | Α   | _                | _              | _               | 25 | В   | _                | _              | _               |

| 10                                           | Α   | _                | _              | _               | 26 | В   | _                | _              | _               |

| 11                                           | Α   | _                | _              | _               | 27 | В   | _                | _              | _               |

| 12                                           | Α   | _                | _              | _               | 28 | В   | _                | _              | _               |

| 13                                           | Α   | _                | _              | _               | 29 | В   | _                | _              | _               |

| 14                                           | Α   | _                | _              | _               | 30 | В   | _                | _              | _               |

| 15                                           | Α   | _                | _              | _               | 31 | В   | _                | _              | _               |

| 16                                           | Α   | _                | _              | _               | 32 | В   | _                | _              | _               |

| Table 11. EPM5130 I/O Pin-Outs (Part 2 of 2) |     |                  |                |                 |     |     |                  |                |                 |

|----------------------------------------------|-----|------------------|----------------|-----------------|-----|-----|------------------|----------------|-----------------|

| MC                                           | LAB | 84-Pin<br>J-Lead | 100-Pin<br>PGA | 100-Pin<br>PQFP | MC  | LAB | 84-Pin<br>J-Lead | 100-Pin<br>PGA | 100-Pin<br>PQFP |

| 33                                           | С   | 22               | C2             | 31              | 49  | D   | 30               | G3             | 41              |

| 34                                           | С   | 25               | C1             | 32              | 50  | D   | 31               | G1             | 42              |

| 35                                           | С   | 26               | D2             | 33              | 51  | D   | 32               | Н3             | 45              |

| 36                                           | С   | 27               | D1             | 34              | 52  | D   | 33               | J1             | 46              |

| 37                                           | С   | 28               | E2             | 35              | 53  | D   | 34               | J2             | 47              |

| 38                                           | С   | 29               | E1             | 36              | 54  | D   | 35               | K1             | 48              |

| 39                                           | С   | _                | F1             | 39              | 55  | D   | _                | K2             | 49              |

| 40                                           | С   | _                | G2             | 40              | 56  | D   | _                | L1             | 50              |

| 41                                           | С   | _                | _              | _               | 57  | D   | _                | _              | _               |

| 42                                           | С   | _                | _              | _               | 58  | D   | _                | _              | _               |

| 43                                           | С   | _                | _              | _               | 59  | D   | _                | _              | _               |

| 44                                           | С   | _                | _              | _               | 60  | D   | _                | _              | _               |

| 45                                           | С   | _                | _              | -               | 61  | D   | _                | _              | _               |

| 46                                           | С   | _                | _              | _               | 62  | D   | _                | _              | _               |

| 47                                           | С   | _                | _              | _               | 63  | D   | _                | _              | _               |

| 48                                           | С   |                  | _              | _               | 64  | D   |                  |                |                 |

| 97                                           | G   | 64               | L12            | 81              | 113 | Н   | 72               | G11            | 91              |

| 98                                           | G   | 67               | L13            | 82              | 114 | Н   | 73               | G13            | 92              |

| 99                                           | G   | 68               | K12            | 83              | 115 | Н   | 74               | F11            | 95              |

| 100                                          | G   | 69               | K13            | 84              | 116 | Н   | 75               | E13            | 96              |

| 101                                          | G   | 70               | J12            | 85              | 117 | Н   | 76               | E12            | 97              |

| 102                                          | G   | 71               | J13            | 86              | 118 | Н   | 77               | D13            | 98              |

| 103                                          | G   | _                | H13            | 89              | 119 | Н   | _                | D12            | 99              |

| 104                                          | G   | _                | G12            | 90              | 120 | Н   | _                | C13            | 100             |

| 105                                          | G   | _                | _              | _               | 121 | Н   | -                | _              | _               |

| 106                                          | G   | _                | _              | -               | 122 | Н   | _                | _              | _               |

| 107                                          | G   | _                | _              | -               | 123 | Н   | _                | _              | _               |

| 108                                          | G   | _                | _              | -               | 124 | Н   | -                | -              | _               |

| 109                                          | G   | _                | _              | -               | 125 | Н   | _                | _              | _               |

| 110                                          | G   | _                | _              | -               | 126 | Н   | -                | -              | _               |

| 111                                          | G   | _                | _              | -               | 127 | Н   | _                | _              | _               |

| 112                                          | G   |                  | _              | _               | 128 | Н   |                  | _              |                 |

| Table 12. EPM5192 Dedicated Pin-Outs |                                |                                  |  |  |  |  |  |

|--------------------------------------|--------------------------------|----------------------------------|--|--|--|--|--|

| Pin Name                             | 84-Pin J-Lead                  | 84-Pin PGA                       |  |  |  |  |  |

| INPUT/CLK                            | 1                              | A6                               |  |  |  |  |  |

| INPUT                                | 2, 41, 42, 43, 44, 83, 84      | A5, K6, J6, J7, L7, C7, C6       |  |  |  |  |  |

| GND                                  | 18, 19, 39, 40, 60, 61, 81, 82 | A7, B7, E1, E2, G10, G11, K5, L5 |  |  |  |  |  |

| VCC                                  | 3, 24, 45, 66                  | B5, E10, G2, K7                  |  |  |  |  |  |

| MC | LAB | 84-Pin<br>J-Lead | 84-Pin<br>PGA | MC | LAB | 84-Pin<br>J-Lead | 84-Pin<br>PGA |

|----|-----|------------------|---------------|----|-----|------------------|---------------|

| 1  | Α   | 4                | C5            | 17 | В   | 12               | C2            |

| 2  | Α   | 5                | A4            | 18 | В   | 13               | B1            |

| 3  | Α   | 6                | В4            | 19 | В   | 14               | C1            |

| 4  | Α   | 7                | А3            | 20 | В   | 15               | D2            |

| 5  | Α   | 8                | A2            | 21 | В   | _                | _             |

| 6  | Α   | 9                | В3            | 22 | В   | _                | _             |

| 7  | Α   | 10               | A1            | 23 | В   | _                | _             |

| 8  | Α   | 11               | B2            | 24 | В   | _                | _             |

| 9  | Α   | _                | _             | 25 | В   | _                | _             |

| 10 | Α   | _                | _             | 26 | В   | _                | _             |

| 11 | Α   | _                | _             | 27 | В   | _                | _             |

| 12 | Α   | _                | _             | 28 | В   | _                | _             |

| 13 | Α   | _                | _             | 29 | В   | _                | _             |

| 14 | Α   | _                | _             | 30 | В   | _                | _             |

| 15 | Α   | _                | _             | 31 | В   | _                | _             |

| 16 | Α   | _                | _             | 32 | В   | _                | _             |

| Table 13 | Table 13. EPM5192 I/O Pin-Outs (Part 2 of 4) |                  |               |    |     |                  |               |  |

|----------|----------------------------------------------|------------------|---------------|----|-----|------------------|---------------|--|

| MC       | LAB                                          | 84-Pin<br>J-Lead | 84-Pin<br>PGA | MC | LAB | 84-Pin<br>J-Lead | 84-Pin<br>PGA |  |

| 33       | С                                            | 16               | D1            | 49 | D   | 22               | G3            |  |

| 34       | С                                            | 17               | E3            | 50 | D   | 23               | G1            |  |

| 35       | С                                            | 20               | F2            | 51 | D   | 25               | F1            |  |

| 36       | С                                            | 21               | F3            | 52 | D   | 26               | H1            |  |

| 37       | С                                            | _                | _             | 53 | D   | _                | _             |  |

| 38       | С                                            | _                | -             | 54 | D   | _                | _             |  |

| 39       | С                                            | _                | -             | 55 | D   | _                | -             |  |

| 40       | С                                            | _                | -             | 56 | D   | _                | _             |  |

| 41       | С                                            | _                | _             | 57 | D   | _                | _             |  |

| 42       | С                                            | _                | _             | 58 | D   | _                | _             |  |

| 43       | С                                            | _                | _             | 59 | D   | _                | _             |  |

| 44       | С                                            | _                | -             | 60 | D   | _                | -             |  |

| 45       | С                                            | _                | _             | 61 | D   | _                | _             |  |

| 46       | С                                            | _                | -             | 62 | D   | _                | -             |  |

| 47       | С                                            | _                | _             | 63 | D   | _                | _             |  |

| 48       | С                                            | _                | -             | 64 | D   | _                | -             |  |

| 65       | Е                                            | 27               | H2            | 81 | F   | 31               | L1            |  |

| 66       | Е                                            | 28               | J1            | 82 | F   | 32               | K2            |  |

| 67       | Е                                            | 29               | K1            | 83 | F   | 33               | K3            |  |

| 68       | Е                                            | 30               | J2            | 84 | F   | 34               | L2            |  |

| 69       | Е                                            | _                | -             | 85 | F   | 35               | L3            |  |

| 70       | Е                                            | _                | _             | 86 | F   | 36               | K4            |  |

| 71       | Е                                            | _                | _             | 87 | F   | 37               | L4            |  |

| 72       | Е                                            | _                | -             | 88 | F   | 38               | J5            |  |

| 73       | Е                                            | _                | _             | 89 | F   | _                | _             |  |

| 74       | Е                                            | _                | -             | 90 | F   | _                | -             |  |

| 75       | Е                                            | _                | -             | 91 | F   | _                | -             |  |

| 76       | E                                            | _                | _             | 92 | F   | _                | _             |  |

| 77       | Е                                            | _                | -             | 93 | F   | _                | -             |  |

| 78       | Е                                            | _                | -             | 94 | F   | _                | -             |  |

| 79       | Е                                            | _                | _             | 95 | F   | _                | _             |  |

| 80       | E                                            | _                | -             | 96 | F   | -                | -             |  |

| MC  | LAB | 84-Pin<br>J-Lead | 84-Pin<br>PGA | MC  | LAB | 84-Pin<br>J-Lead | 84-Pin<br>PGA |

|-----|-----|------------------|---------------|-----|-----|------------------|---------------|

| 97  | G   | 46               | L6            | 113 | Н   | 54               | J10           |

| 98  | G   | 47               | L8            | 114 | Н   | 55               | K11           |

| 99  | G   | 48               | K8            | 115 | Н   | 56               | J11           |

| 100 | G   | 49               | L9            | 116 | Н   | 57               | H10           |

| 101 | G   | 50               | L10           | 117 | Н   | _                | _             |

| 102 | G   | 51               | K9            | 118 | Н   | _                | _             |

| 103 | G   | 52               | L11           | 119 | Н   | _                | _             |

| 104 | G   | 53               | K10           | 120 | Н   | _                | _             |

| 105 | G   | _                | _             | 121 | Н   | _                | _             |

| 106 | G   | _                | _             | 122 | Н   | _                | _             |

| 107 | G   | _                | _             | 123 | Н   | _                | _             |

| 108 | G   | _                | _             | 124 | Н   | _                | _             |

| 109 | G   | _                | _             | 125 | Н   | _                | _             |

| 110 | G   | _                | _             | 126 | Н   | _                | _             |

| 111 | G   | _                | _             | 127 | Н   | _                | _             |